Freescale Semiconductor DSP56364 manuals

Owner’s manuals and user’s guides for Processors Freescale Semiconductor DSP56364.

We providing 1 pdf manuals Freescale Semiconductor DSP56364 for download free by document types: User Manual

Freescale semiconductor DSP56364 User Manual (184 pages)

Brand: Freescale-semiconductor | Category: Processors | Size: 1.91 MB |

Table of contents

Contents

3

1 Overview

19

1.2 Features

20

DSP56364

30

2.2 Power

31

2.3 Ground

31

After RESET

34

Memory Maps

49

Introduction

66

Normal Mode

81

Network Mode

81

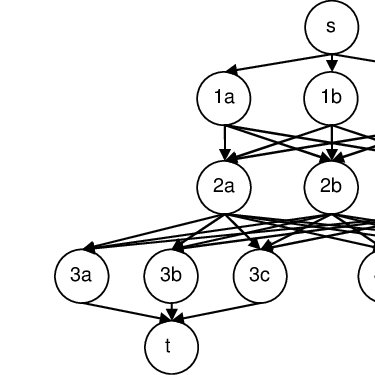

Figure 6-14

82

Operating Modes

110

7.4.4.2 HSAR I

123

7.6.1 Overview

133

C Slave Mode

137

C Master Mode

139

Bits XTLR and

169

SHI Host Receive

171

Freescale Semiconductor devices